浏览次数:6880

发布时间:2022-09-29 09:07:25

编辑:鱼蛋科服

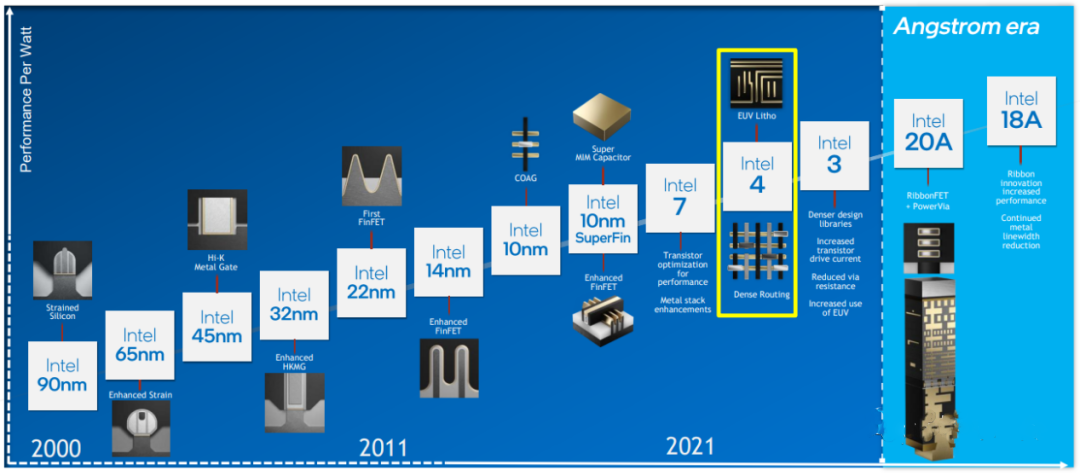

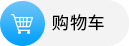

在2019年初,英特尔终于公开承认他们搞砸了——他们雄心勃勃的10纳米工艺失败了。这主要归因于其疯狂的密度改进目标以及太多新颖的技术特征证明。伺候,该公司承诺通过更平衡的PPA和衡量的风险承担恢复到更规律的节点更新节奏来纠正这一问题。历经两次的CEO更换,在Gelsinger的监督下,我们终于看到了芯片巨头为重回正轨所做的一些努力。

在本周早些时候在夏威夷举行的2022年IEEEVLSI技术和电路研讨会上,英特尔展示了许多涉及其英特尔4工艺的论文。这些论文主要由英特尔公司技术开发副总裁BenSell发表。

Intel4

这个新节点称为Intel4。出于所有实际目的,它是适当的10纳米继任者。换句话说,如果它在2020年发布,它应该被正确地称为“7nm”。今天,它被称为“Intel4”,是“Intel7”(以前称为“10nmEnhancedSuperFin”,以前称为“10nm++”)的继任者。

Intel4很好但很奇怪,真的很奇怪。在时间方面,英特尔预计这一制程将在今年晚些时候加速——这意味着会是明年产品使用的工艺。如果一切按计划进行,Intel4的继任者“Intel3”将在几乎整整一年之后(2023年底开始升级)。这应该开始让您了解英特尔如何看待这个制程。

在深入研究细节之前,我们想强调一下Intel4并非设计为一个典型的成熟(full-fledged)节点。虽然它是一个高容量(high-volume)节点,但它可以在其上制作的内容非常有限(因此可能会大大限制其容量)。例如。它不会提供许多您通常会从英特尔节点看到的大型库,例如高密度和中档性能密度库,这些库对图形和其他应用程序等事物很重要,但对CPU核心设计来说,这并不重要。

从这个角度看,英特尔的这个节点是为为那些想把使用不同工艺的chiplet合封到一起的computetile而准备的。

从小处着手,让它发挥作用,建立起来

Intel4代表了公司处理其节点设计方式的范式转变。

从历史上看,该公司专注于推出传统上所谓的全节点——大约每两年推出一个节点,带来整整一代的改进。代工厂(例如,台积电以及十年前的富士通、东芝、NEC等)过去常常引入称为半节点的后续节点,这将进一步改进节点以及较小的间距缩放。

前提很简单:扩展和增强现有的高收益节点既便宜又容易。

而传统的“全节点”和“半节点”模型被淘汰了。随着最近FinFET节点的复杂性激增,代工厂转向新的“nodelet”方案。在此模型下,首先引入一个基本节点(例如,7LPP或N7),然后由一个或多个增强节点(nodelet)接替,几乎每年都会带来微小但增量的变化(例如,N7P、N7+、N6,6LPP)。

快速接替Intel4的是Intel3,预计将在明年年底推出。该公司表示,该制程将引入新的库,在密度、功率和性能方面都比Intel4有所提高。此外,Intel4与Intel3向前兼容,使设计迁移更容易。更重要的是,Intel3将拥有完整的代工产品。

在许多方面可以看出,英特尔都在借鉴代工手册。很明显,他们正在限制Intel4特性和功能的复杂性以降低风险。此外,他们今年推出Intel4的能力将对他们明年按时将Intel3推向市场的能力发挥重要作用,而正确执行是最重要的。他们的目标是构建更广泛、改进的功能组合、库、和其他IP,这在成熟的制程中要容易得多,并且这是解决此问题的正确方法。鉴于Intel3被定位为英特尔代工服务(IFS)的初始旗舰节点,这一点至关重要。

由于Intel4的范围有限,并且其快速跟进的成熟Intel3节点具有全节点密度/PPA特性,我们认为最好将Intel4视为临时权宜之计节点。

产品

最初,英特尔透露MeteorLake客户端SoC和GraniteRapids数据中心SoC都将在Intel4工艺上制造。然而,在今年早些时候的公司2022年投资者会议上,该公司宣布GraniteRapids的制造工艺将从Intel4升级到Intel3制程。出于我们今天对Intel4和Intel3之间关系的了解,这种切换对于GraniteRapids来说更有意义。

在诸如IEEEVLSISymposium等技术会议上,英特尔通常将其演讲的范围仅限于其工艺的技术方面。在这个相当罕见和不寻常的场合,Sell谈到了即将推出的第一款Intel4产品——MeteorLake。采用Intel4的MeteorLake将成为3Dfoveros封装技术的量产产品。Intel4支持最新的封装技术,并为Foveros提供了更激进的微凸点间距——从50μm扩展到36μm。MeteorLake包含一个图形tiles、SoCtiles、计算tiles和I/Otiles,所有这些都位于一个Si中介层上。MeteorLake封装和dieshot如下所示。

制程概述

Intel4(连同其增强版Intel3)是Intel最后一个基于FinFET的节点。在高层次上,这是继22nm、14nm和10nm之后第四个使用FinFET的主要节点。据说该工艺利用了第二代COAG和第二代单虚拟门(singledummygate)。英特尔声称新的Intel4工艺为高性能库提供了大约2倍的面积扩展。最后,值得强调的是,这是该公司的首个EUV支持的工艺,有望显著简化工艺。

极紫外(EUV)光刻

自对准四边形图案(SAQP)

有源栅极接触(COAG)

单虚拟门(SDB)

增强型铜互连

在晶体管级别,各种间距适度缩小。例如,与Intel7相比,Intel4的鳍片间距为30纳米,栅极间距为50纳米,分别缩小了0.83倍和0.88倍。互连堆栈经历了一些更重要的变化,包括材料变化。例如,M0金属间距经历了较大的间距从40nm缩小到30nm或0.75倍。

在进一步讨论之前,我们想重申一下,由于使用该节点的产品有限,Intel4将仅提供高性能单元库。通常,英特尔至少为逻辑设计了三个标准库。例如,使用英特尔10nm,该公司拥有高密度单元、高性能/移动性能单元和超高性能单元。虽然它们使用相同的底层晶体管,但它们的特点是性能、功率和密度特性是pMOS和nMOS器件的函数。对于FinFET器件,这是鳍片数量的直接函数。因此,英特尔10nm具有每个器件可容纳2个鳍的HD单元、每个器件可容纳3个鳍的HP单元和每个器件可容纳4个鳍的UHP单元。

扩展(Scaling)是DTCO-Heavy

正如我们在过去几个节点中看到的那样,PPA目标现在在很大程度上都涉及DTCO。Intel4也不例外。事实上,如果我们将intel7单元转移到intel4上并仅调整间距,我们将获得1.22倍的晶体管密度改进或大约0.82倍的缩放。这意味着,DTCO不是pitch缩放,而是intel4中密度改进的绝大部分。

许多关键技术在这里发挥作用。

首先,intel4使用第二代COAG和第二代单虚拟门,允许它们随着新的栅极和鳍片间距进行扩展,同时保持单元高度和单元宽度的优势,从而实现我们在intel7中看到的密度改进。以前,英特尔在nMOS和pMOS器件之间的区域(栅极输入的前接触区域)有两条扩散线(diffusionlines)的间距。Intel4利用了单元的这一区域并消除了其中一条扩散线,从而缩短了单元高度并获得了宝贵的空间。我们估计仅此一项就产生了大约11.5%的面积缩放。

最后,由于其更高的性能,intel4经历了4:3的鳍片减少。这是对整体面积额外缩小25%的最大贡献。总而言之,DTCO在传统pitch缩放的基础上增加了1.5倍的缩放。这证明了DTCO在现代前沿节点中的重要性,以及STCO将如何在引入未来技术(如埋入式电源轨和背面供电网络)中发挥更大的作用。

为了促进鳍的减少,必须增强设备性能。对于Intel4,该公司报告称,nMOS和pMOS的驱动电流均超过每微米2mA。对于0.7V的nMOS,驱动电流为每微米2.25mA,漏电流为每微米20nA。同样,对于pMOS,在相同泄漏情况下,每微米的驱动电流为2mA。这些数字代表了比10纳米设备大约25-30%的改进。

Intel4提供8个阈值(threshold)电压器件(4nMOS/8pMOS)。与Intel7相比,这些新设备提供了额外5%的功率不受限制的性能提升。

英特尔还报告了一些使用标准可授权内核(可能是Cortex-A7x内核)的功率性能数据。下面的电源频率图展示了在intel7与intel4上制造相同内核的对比情况。在低电压下,英特尔报告在等功率下的频率比intel7提高了20%以上。或者,在相同的低电压下,相同的内核结果在等频处能量减少约40%。

密度

综上所述,英特尔表示,根据内部估计,他们看到从intel7到intel4的完整高性能库扩展为2倍。

像往常一样,WikiChip根据当前公开的代工数据生成自己的独立估计。

我们自己的估计表明,intel4的密度比英特尔7/10nm提高了1.83倍。但是,我们的估计还表明,intel4提供的密度比intel7提高了2.04倍。这是怎么算出来的?答案实际上在英特尔自己的VLSI演示幻灯片中。

随着10纳米SuperFin及其后继产品增强型SuperFin(现在称为Intel7)的推出,英特尔推出了一种具有60纳米多晶间距的新型晶体管,以实现更高的驱动电流性能。在生产性能显著提高的晶体管的同时,它的不利影响是将逻辑密度降低了0.9倍。值得注意的是,这些cell被用于AlderLake中的GoldenCove和Gracemont核心。

为此,我们估计intel4密度为123.4MTr/mm²,是英特尔7中60.5MTr/mm²的2.04倍。我们对TSMCN5的数据非常不完整,但我们基于已知间距的粗略估计将其HP库为94.85MTr/平方毫米。根据最近公开的大多数代工数据,intel4HP单元似乎比TSMCN5HP更密集,并且可能更接近或优于TSMCN3HP单元,并且比三星的3GAE更密集。鉴于过去三年10nm对公司造成的动荡,以这样的数字出现是相当令人惊讶的。它还强烈表明intel3可以匹配并超越即将推出的3nm级代工产品。

互连

Intel4互连堆栈经历了相当大的变化。

Intel4的基本设计规则的一个亮点如下所示,与具有17个金属层的Intel7相比,Intel4增加了一层。M4上方的大多数互连都看到了通常的间距缩小,其中大部分在0.7x-0.85x缩放左右。与之前的节点一样,两个顶层是厚金属层。与大多数其他wires相比,英特尔大幅缩小了最后一层厚金属层。最受关注的区域是前四个路由层(routinglayers)。在那里,不仅某些间距没有缩小,有些实际上变宽了。这些层也经历了新的材料变化。

尽管英特尔没有详细说明确切的层,但EUV和SAQP都以最紧密的间距使用。此外,使用单一镶嵌(damascene)工艺来形成M0轨道的触点,这可能有助于在该步骤中形成EUV图案。

四个最低金属层在两个正交方向上横跨芯片,用于cell本地电源和路由。在Intel4中,它们具有非常规则的pitches。为什么有些间距缩小而其他间距变宽似乎有一个很好的理由,这主要与单元布局优化有关。

在Intel7中,M1层非常激进的鳍片间距意味着该公司采用了3:2的间距比。这有一些奇怪的副作用。在Intel4中,英特尔实际上将间距缩小了近1.4倍,以通过相同的间距将其固定到门上。正如我们将在下面展示的那样,这不仅简化了设计,而且完全消除了布局的一些不合适。英特尔似乎对M3层做了同样的事情。我们在这里的最后观察涉及也与鳍平行的M2和M4层。这些具有2:3的比例。

正如我们之前提到的,在Intel7中,该公司选择了非常激进的M1间距——36nm。该轨道(track)平行于多边形轨道。选择该间距是为了便于金属层和栅极间距之间的比率为3:2。换句话说,更紧密的间距允许每个单元的每个poly有更多的M1轨道,这意味着更多的引脚命中位置。这种设计提供了更好的单元间连接和更好的块级访问。不幸的是,在M1处具有此比率也会导致一些单元级别的奇怪,其中取决于cellpolycount的均匀/奇数,您最终可能会得到左对齐或右对齐的单元格。解决这个问题意味着减少面积利用率。

为了简单起见,Intel4显然完全放弃了该方案。M1和M3层现在都与poly挂钩,完全消除了这种错位问题。有趣的是,该公司还将M0轨道固定在鳍上。那些垂直于多边形。在Intel7中具有44nm和52nm间距的上M2和M4层在Intel4中都具有45nm。从布局的角度来看,选择45nm是非常清楚的,因为它们现在以2:3的比例固定在鳍片上。请记住,由于单元格高度是一个固定属性,因此在该方向上没有对齐问题。

在VLSI上,英特尔还讨论了intel4引入的新网格互连架构。在之前的节点中,英特尔定义了通孔和trackendcaps的最小间距。但是,没有具体说明它们的确切位置。这导致了大量的patterns,由于增加的patterns可变性而引入了新的分析复杂性层。在Intel4中,线端和过孔现在严格放置在网格上,从而减少了可能的放置。据说新的简单网格限制通过减少图案可变性以及通过更好地识别问题和优化自动布局布线(APR)设计流程来提高良率。

铜回来了

当英特尔首次推出他们的10纳米工艺时,他们宣布推出新的互连材料——钴。主要动机是其更好的电迁移特性。随着我们继续缩小互连,铜互连的高电阻率衬垫和阻挡层的厚度基本保持不变(thethicknessofthehigh-resistivitylinerandbarrierforthecopperinterconnectsstayedaboutthesame)。这主要是由于工程上难以将其减薄到比现有的几纳米更小。最终结果是,随着wires规模的提升,屏障(barrier)本身开始在互连横截面积中占据越来越大的份额。随着High-resistivitybarriers慢慢构成互连的大部分,它开始主导导线本身的电阻率。

虽然由于钴及其更薄的衬里,在10nm工艺上,两个局部互连层(M0和M1)处的wire电阻确实增加了,但英特尔报告称线路电阻降低了2倍。此外,这两层也使电迁移提高了5-10倍。但最终,英特尔似乎在Intel4中退出了钴。钴是一种更难使用的材料,并且被推测是导致其良率难以提升的根源之一。

在下图中,英特尔展示了intel7与具有钽阻挡层(Tantalumbarrier)的纯钴内核与具有氮化钽阻挡层(Tantalumnitridebarrier)的传统铜合金内核之间的关系。这两个选项具有互补的属性。纯Co提供了相当好的电迁移特性,但提供了更差的线路电阻。同样,Cu合金提供更好的线路电阻但更差的电迁移寿命。事实上,与纯钴相比,铜合金提供了0.75倍的线路电阻,这是相当大的电阻下降。对于Intel4,该公司选择在最低的四个金属层中使用增强型铜(eCu)。这种增强的铜线包括一个钽阻挡层,而在纯铜芯周围也有钴包层。

内存

与仍然提供双倍晶体管密度的逻辑缩放不同,内存缩放正在面临严峻挑战。

Intel4引入了两个标准的6TSRAM单元——高密度和大电流单元。高密度(PU:PG:PD=1:1:1)cell从0.0312平方微米缩小到0.0240,而高性能(PU:PG:PD=1:2:2)cell缩小到0.0300平方微米.这些cell分别看到了0.77倍和0.68倍的缩放比例,这与我们过去看到的约0.6倍的历史缩放比例相去甚远。除了6T单元之外,英特尔还开发了一个8TSRAM位单元,它在6T写入端口的基础上增加了一个3鳍读取端口,总面积为0.0360平方微米。虽然占用1.74倍的面积,但它使用的读/写能量分别比HDC和HCC低6倍和12倍。

将Intel4的密度与台积电和三星的代工产品进行比较时,英特尔4SRAM的尺寸实际上相当令人失望。对于我们在这里的密度估计,我们使用我们的标准等辅助电路开销方法,该方法可能与公司自己报告的数字不同。为此,intel4HDC产生了大约27.8Mib/mm²的内存密度。与密度为31.8Mib/mm²的TSMCN5SRAM相比,英特尔的密度大约低14.5%。

英特尔还展示了其intel4SRAMshuttle测试芯片。testvehicle具有57Mib的高密度cell和50Mib的高性能cell。硅测量表明,高密度cell的90%Vim工作电压(percentileVimoperation)为0.6V,高性能cell的工作电压为0.55V。

电容器

intel4还改进了intel7的MIM电容器。intel4上的新MIMcap提供了令人印象深刻的两倍于intel7的电容,达到376fF/μm²。

在经历了五年的制造问题折磨之后,英特尔终于出现了复苏的迹象。

在2022年IEEEVLSI技术和电路研讨会上,英特尔终于公布了他们的下一代领先的高性能工艺节点——intel4。该节点预计将在今年年底前量产。虽然在功能方面不如他们通常的节点那么全面,但intel4提供了足够的功能来支持他们的下一代客户端SoC(代号MeteorLake)所需的计算块。该节点充分利用EUV并提供比Intel7大约20%的性能/瓦特增益。

在SoC级别,该节点在等频下可降低多达40%的功率或在等频下提供>20%的频率提升-力量。此外,该节点的高性能库拥有完整的2.04倍密度缩放,超过intel7中用于AlderLake的最高性能单元。在纸面上,这些PPA特性使公司的新intel4工艺的性能水平优于台积电N3和三星3GAE。在密度方面,英特尔4与N3高性能库相比似乎极具竞争力。

很明显,Intel4是经过精心制作的。仔细的标准单元缩放以及架构简化有助于降低工艺复杂性。随着EUV的引入,回归到更简单的材料有助于大大减少掩模、步骤和图案的可变性和复杂性。英特尔表示,与英特尔7相比,新节点还大大降低了每个晶体管的成本。

尽管如此,我们认为英intel4是一个权宜之计节点——一个最小可行的产品,是通往intel3的中间节点,这预计将发生在intel4之后大约一年(明年年底)。Intel3将是Intel的最终FinFET工艺。此后的一切都将使用该公司称为RibbonFET的新的环栅晶体管架构。intel3恰好也是英特尔代工服务(IFS)即将推出的旗舰节点。intel3建立在intel4的基础上,这就是为什么及时正确地将intel4提升到良好的良率和高产量如此重要的原因。该公司已经透露,intel3将再提供18%的性能/瓦特改进,这本身就是一个全节点改进。该过程还将引入一个新的更密集的高性能库以及一组更完整的其他库和IP。

从本文详述的Intel4工艺,该公司能否重新获得其在半导体行业的领先地位,完全取决于其执行力。

中文(中国)

中文(中国)

中文(中国)

中文(中国)