中文(中国)

中文(中国)

- English

- 中文(中国)

- Русский

- 한국어

- עִבְרִית

中文(中国)

中文(中国)

Tessent

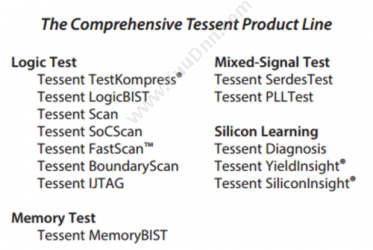

The flexibility of the Tessent product line enables high quality tests to be applied throughout the product life cycle—from wafer and package test to burn-in, in-system, and field test. Accurate yield analysis is achieved by exploiting the structural nature of scan test and BIST methodologies and correlating to physical features.

The full Tessent product suite combines deterministic scan testing, embedded pattern compression, built-in self test, specialized embedded memory test and repair, and boundary scan, mixed-signal test, and silicon learning technologies.

Tessent TestKompress automatic test pattern generation (ATPG) delivers the highest quality scan test with the lowest manufacturing test cost. Its industry-proven ATPG engine offers 100x or better test compresstion and targets all the fault models necessary for thorough silicon test.

Tessent LogicBIST is a vectorless high-quality logic test solution that provides complete corelevel test handoff, full test reuse throughout the product life cycle, quick and robust hand-off to manufacturing test and enables fast test bring-up.

Tessent TestKompress and LogicBIST can also be used together, in a hybrid approach that shares test logic.

Tessent TestKompress enables full-chip, transistor-level ATPG to directly target defects internal to library cells. This Cell-Aware test capability significantly improves product quality.

The Tessent solution lets you insert wrappers for hierarchical test methodologies and to retarget scan patterns from block level to chip level for effective test reuse. The hierarchical test flow supports integration of any combination of Tessent test IP into any core.

Tessent IJTAG is the first product to provide automation to support the emerging IEEE 1687 standard for plug-and-play IP integration. It helps you connect any number of IEEE 1687 compliant IP blocks into an integrated, hierarchical network and to communicate commands to the blocks from a single toplevel access point.

Tessent MemoryBIST provides a complete solution for at-speed testing, diagnosis, and repair of embedded memories. The solution’s architecture is hierarchical, allowing BIST and self-repair capabilities to be added to individual cores as well as at the top level.

Tessent MemoryBIST provides at-speed testing of 3D stacked memory die with support for all popular DRAM protocols, including those supporting the common JEDEC WideIO interface standard.

The Tessent mixed-signal solutions provide complete, parametric, embedded test for PLLs, DLLs, and multi-Gb/s SerDes. The solutions measure waveshape, many types of jitter, and other important performance parameters.