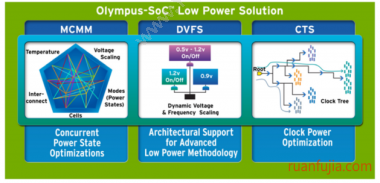

Olympus-SoC is a comprehensive netlist-to-GDSII physical design implementation platform.

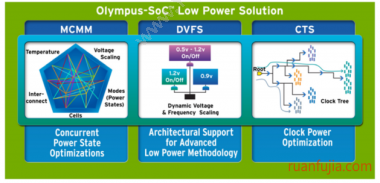

The Olympus-SoC low-power platform is the first place-and-route system to offer true concurrent multi-corner, multi-mode closure for both power and timing, giving best quality of results and fast turnaround time for the largest designs at 45 nm and below.

Key Features :

Design Planning

- Design planning including flat, hierarchical, and pseudo flat floorplanning

- Support for both channel-less and channelbased flows

- Timing and congestion aware pin placement and feed-through insertion

- Data flow graph driven automatic macro placement

- Timing-driven placement engine for optimal QoR

- Powerful and efficient GUI

Flexible Routing

- Native coloring, verification and conflict resolution

- DRC and DFM rule support for all key nodes and foundries

- Intelligent conflict double/multi-patterning resolution engine

- Pattern matching and recommended rules support

- Variation-aware timing and SI driven routing

Low Power

- UPF 2.0 (IEEE 1801) based multi-voltage flow

- Power state table (PST) based advanced buffering

- Support for level shifters, isolation cells, and retention registers

- Distributed and ring style multi-threshold (MTCMOS) switch cell insertion

- Hierarchical UPF support

- Power-aware CTS featuring cloning, restructuring, and slew shaping

- Concurrent power and timing optimization for all corner/mode/power scenarios

High Performance

- True and concurrent MCMM optimization during all design STEPS

- Best-in-class MCMM-based CTS

- On-chip variation (OCV) driven CTS and opportunistic 3D clock shielding

- Resistance-aware concurrent cell and wire optimization

- Extremely fast and accurate, on-the-fly parasitic extraction

- Sign-off quality timing analysis and optimization

Area Reduction

- Unified global router based congestion modeling

- Channel-less floorplanning flow

- Intelligent white space management

- Precision DP fixing for minimal perturbation

- Dynamic area recovery throughout the flow

- Proprietary density management

TAT Reduction

- Distributed and multithreaded analysis and optimization

- Signoff physical verification during implementation with Calibre InRoute

- Minimal ECO iterations through MCMM optimization

- Signoff quality built-in timing and extraction engines

- Industry’s first multi-threaded timing engine

Highest Capacity

- Compact database and flexible architecture

- Ability to handle 100+ million instance designs

- Flexible abstraction capabilities including SI-ILM, HTP, and black boxes

- Unique synchronized optimization at the top-level design

- Advanced memory reduction technologies

中文(中国)

中文(中国)

中文(中国)

中文(中国)